Case Study: Sizing A Design

Last Edit July 22, 2001

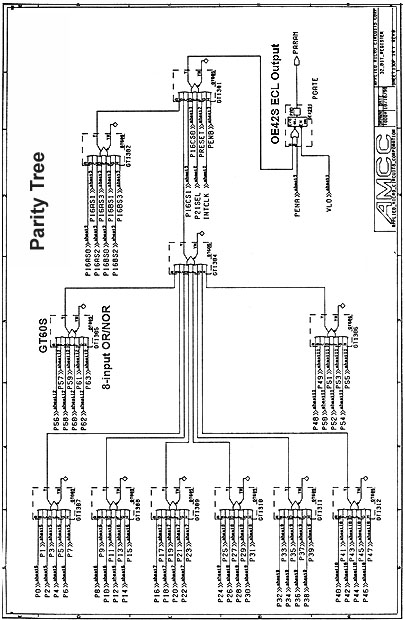

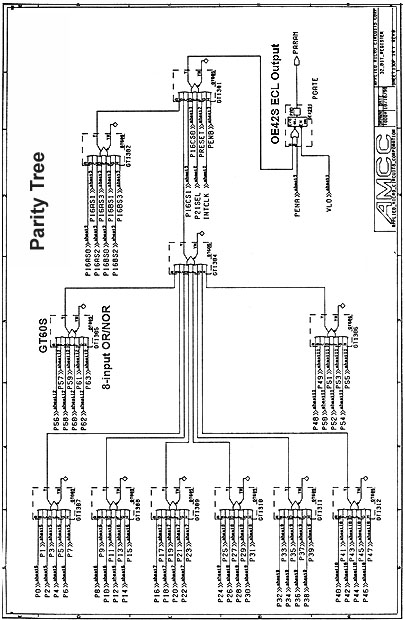

Parity tree

A parity tree of all inputs (required for parametric VIL, VIH testing)

can be formed from NOR gates using the GT60L or GT60S, an 8-input NOR

macro. The L-option is slower and uses less power. The speed of the gate

tree is not important since testing is functional at 100ns intervals.

The first estimate for the tree is to use eleven GT60S macros in a three-level

structure to accommodate the 79 input signals. (The 78 data signals plus

the clock are required.) The parity tree is shown in Figure A-8.

Figure A-8 Parity Tree

|